# A microelectrónica do silício

#### Estrutura da aula

- 1 Perspectiva histórica

- 2 A tecnologia CMOS

- Introdução às técnicas básicas usadas em tecnologia CMOS

- O processo n-well CMOS 2.0 μm

- Definição do n-MOSFET e do p-MOSFET

- As diversas máscaras usadas no CMOS

- Layout físico do inversor

- 3 Regras de layout físico

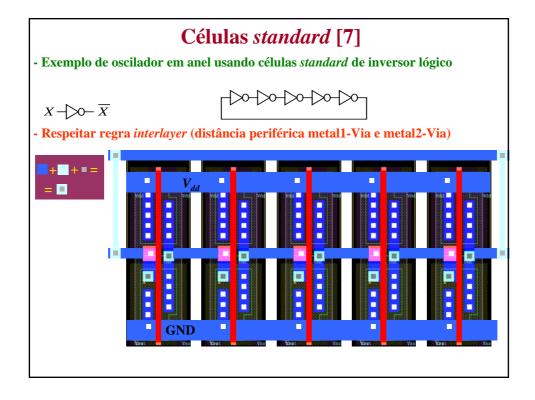

- 4 Células standard

- 5 Elementos parasitas

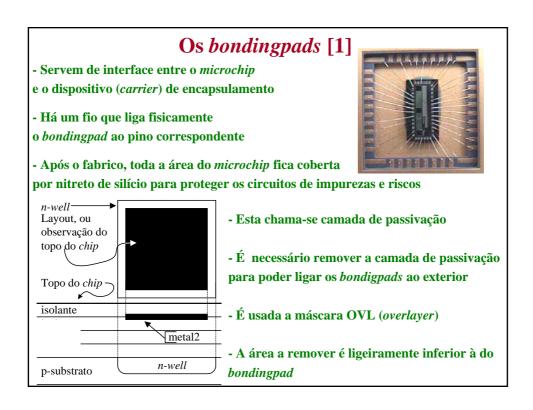

- 6 Bondingpads

## Perspectiva histórica [1]

- A indústria da electrónica é a que apresenta o maior crescimento observado nos últimos anos

- O fabrico de *microchips* com algumas funções lógicas remonta aos anos 60

- Nos anos 60 integrar mais do que um transístor no mesmo corpo semicondutor era considerado um feito

- Nesse tempo, a ideia de fabricar um *microchip* era inconcebivél e mera fantasia

- Os "peritos" defendiam que um *microchip* com 20 transistores para ter probabilidade de funcionamento de 50%, todos os transístores deveriam funcionar com probabilidade de pelo menos 96.59% ( $0.5^{1/20}$ =0.9659)

- Isso não impediu os avanços verificados (microchips com milhões de transístores, como é o caso dos processadores)

## Perspectiva histórica [2]

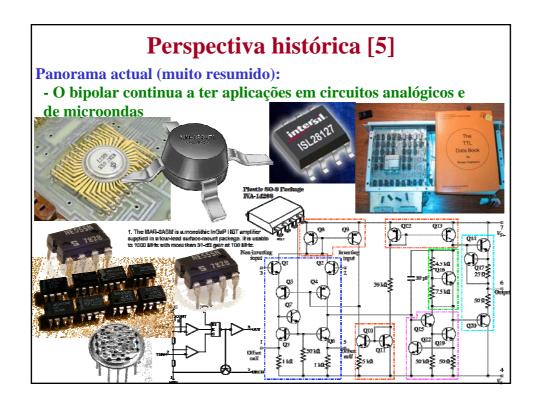

- O Bipolar foi a primeira tecnologia a surgir

- Ainda hoje é utilizada para fabricar os dispositivos 555 e 741

- Até inicio dos anos 80 impôs-se sobre o CMOS

- A difusão dos dopantes é feita em profundidade (3D)

- A contaminação das câmaras limpas não compromete o dispositivo

- Nos anos 70 as câmara não eram suficientemente limpas e uma poeira na superfície do *wafer* era suficiente para inviabilizar o processo de integração CMOS

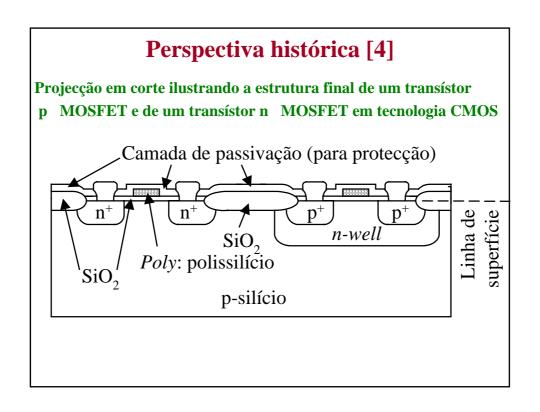

- Para uma melhor percepção dos dois processos veja-se as seguintes projecções em corte

- (1) projecção final para o processo Bipolar

- (2) projecção final para o caso CMOS

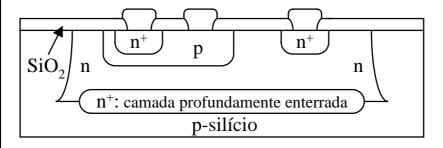

# Perspectiva histórica [3]

Projecção em corte ilustrando a estrutura final de um transístor bipolar NPN em tecnologia bipolar

## Técnicas básicas usadas em tecnologia CMOS [2]

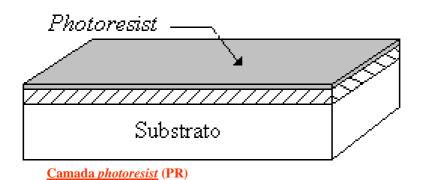

-Uma camada de *photoresist* (PR) é depositada utilizando um disco giratório (*spin coating*), seguindo-se uma cozedura no forno para produzir uma superfície dura.

## Técnicas básicas usadas em tecnologia CMOS [3]

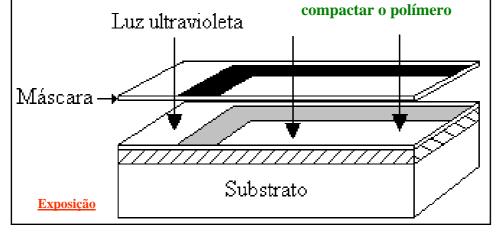

- O PR é um polímero sensível à luz, com propriedades similares a um qualquer filme fotográfico.

- A imagem na máscara é projectada opticamente na superfície do PR durante a exposição aos raios ultravioletas (UV), os quais vão

## Técnicas básicas usadas em tecnologia CMOS [4]

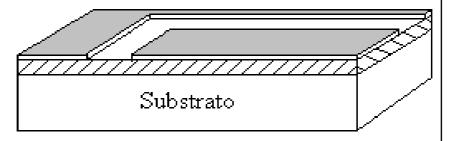

- A área exposta ao raios UV foi compactada

- Um composto químico apropriado remove a área do PR não exposta aos raios UV (neste caso é um PR negativo)

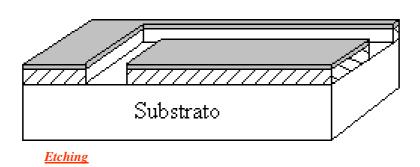

- O desenho da camada PR é usado como máscara para fazer o etching da camada de material. No exemplo, a camada de  $SiO_2$  é removida usando um processo a seco RIE (*Reactive Ion Etching*).

**Reactive Ion Etching** (RIE)

## Técnicas básicas usadas em tecnologia CMOS [5]

- A camada de PR é retirada.

# Técnicas básicas usadas em tecnologia CMOS [6]

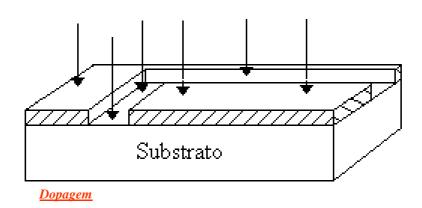

- A superfície do *wafer* é exposta na máquina de difusão (dopagem do silício).

- As áreas do silício expostas são dopadas.

# Técnicas básicas usadas em tecnologia CMOS [7]

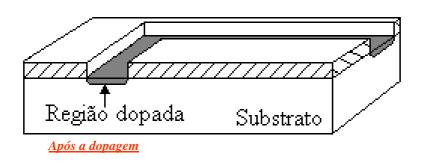

- As áreas do silício expostas são dopadas.

- Resultado da dopagem:

## O processo n-well 2.0 µm [1]

- Trata-se de um exemplo de processo CMOS

- Possui:

- (1) uma camada de polissilício (poly)

- (2) duas camadas de metal

- (3) podem ser fabricados circuitos analógicos, digitais e mistos

Diversos parâmetros do processo CMOS 2.0 µm.

|                                              | n-MOSFET | p-MOSFET | Unidades |

|----------------------------------------------|----------|----------|----------|

| Comprimento mínimo da (gate)                 | 2.0      | 2.0      | μm       |

| Espessura do óxido da gate                   | 25       | 25       | mm       |

| Tensão de threshold                          | 0.75     | -1.10    | V        |

| Minimo pitch para os metais                  | 4.8      | 4.8      | μm       |

| Minimo pitch para a poły                     | 4.0      | 4.0      | μm       |

| Tensão de alimentação nominal                | 5        | 5        | V        |

| I <sub>dso</sub> correntes de saturação para | 4.75     | 1.90     | mA       |

| V <sub>ds</sub> =5 V, V <sub>gs</sub> =5 V   |          |          |          |

## O processo n-well 2.0 µm [1]

- Permite dois tipos de passivos:

- (1) condensadores de precisão e altamente lineares (metal1-poly, metal1-metal2, metal2-poly-metal1)

- (2) Resistências de precisão (poly, Active-SN, Active-SP, metal1, metal2).

- O wafer já pode vir dopado com:

- (1) aceitadores (boro), wafer do tipo p Neste caso:

- (a) os n-MOSFETs são fabricados directamente no wafer

- (b) os p-MOSFETs são fabricados dentro de uma região definida pela máscara *n-well*

- (2) dadores (fósforo), wafer do tipo n

## Fabrico CMOS – Aspectos introdutórios

- Em cada passo, diferentes materiais são depositados ou removidos

- É mais fácil de compreender através da visualização do perfil de um *wafer* e da planta em simultâneo num processo simplificado

- Ferramentas de CAD (*Computer-Aided Design*) para execução de *layout* físico permitem ver todas as camadas simultaneamente.

- Os CADSs mais usados: L-Edit e o Cadence.

- Na sequência litográfica cada camada é aplicada separadamente.

- Para isso é criada uma máscara para cada camada

- A máscara é uma lâmina de vidro onde é aplicado um padrão numa das faces com uma camada fina de crómio.

- A máscara é transparente à luz, excepto nas regiões onde o crómio (regiões negras) não deixa passar a luz.

- As limitações deste processo, tais como a resolução mínima e o espaço mínimo, são definidos por um conjunto de regras de desenho para o *layout* físico.

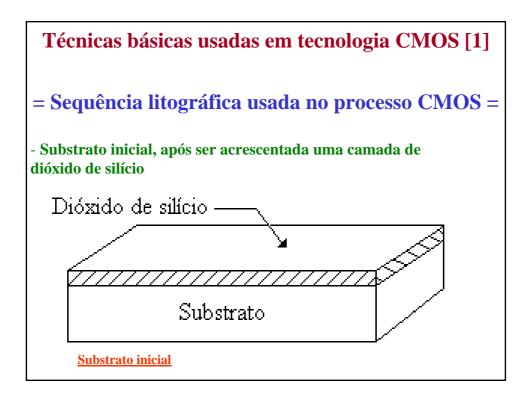

# Fabrico CMOS – Fabrico de um inversor lógico [1]

- O inversor é construído de baixo para cima

- O ponto de partida é usar um *wafer* do tipo p como substrato e depositar por cima uma camada de óxido

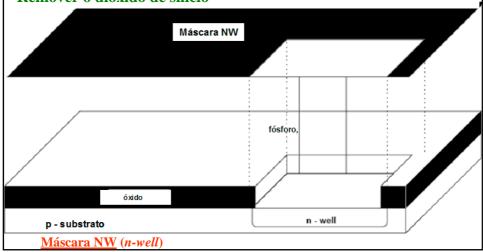

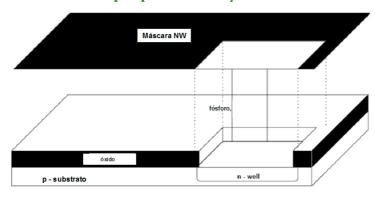

# Fabrico CMOS – Fabrico de um inversor lógico [2] - A máscara NW permite criar a *n-well*

- Assim, após remover a camada onde a n-well deve ficar

- Implantar ou difundir dopantes do tipo n no wafer exposto

- Remover o dióxido de silício

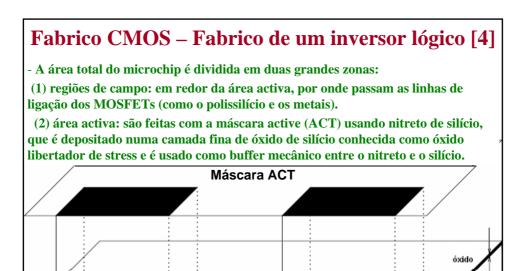

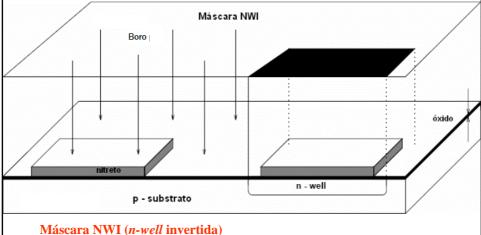

# Fabrico CMOS – Fabrico de um inversor lógico [3]

- Electricamente a zona da n-well deve ser mantida na zona de maior tensão do circuito para garantir o funcionamento adequado.

- Normalmente o *n-well* liga ao  $V_{dd}$ .

- Como a densidade de dispositivos pode ser muito elevada, deve-se ter em atenção o problema do isolamento eléctrico de cada um deles.

- É neste passo do fabrico que é definida a localização de todos os transístores.

- O isolamento é realizado pela próxima colocação de óxido de silício

Máscara ACT (activa ou active)

p - substrato

# Fabrico CMOS – Fabrico de um inversor lógico [5]

- Faz-se uma dopagem com p+ para aumentar a tensão limiar de condução, nas zonas de campo (nas não activas) para garantir:

- (1) o isolamento entre MOSFETs

- (2) evitar que uma tensão aplicada a uma linha de ligação não crie canais indesejáveis

- O óxido LOCOS é depositado por oxidação térmica

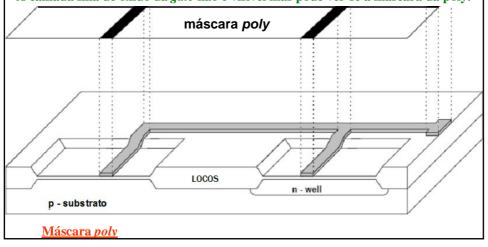

## Fabrico CMOS – Fabrico de um inversor lógico [6]

- O óxido LOCOS é depositado num forno para isolar os MOSFETs

- Remove-se o nitreto de silício e o *wafer* está em condições de ser depositado um óxido (óxido da *gate*) para receber por cima o polissilício.

- O polissilício (que forma as gates) é depositado por CVD.

- A camada fina de óxido da gate não é visível mas pode ver-se a máscara da poly.

# Fabrico CMOS – Fabrico de um inversor lógico [7]

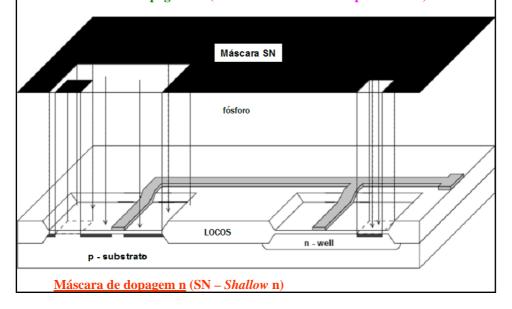

- A máscara SN cria o n-MOSFET (fósforo: n+ nas sources e drains)

- Define as zonas de dopagem n+ (e ainda n+ nos bulks dos p-MOSFET)

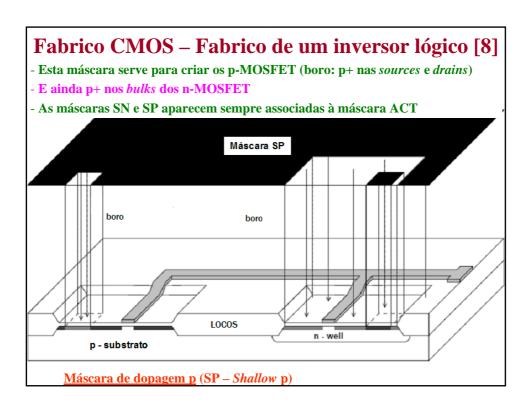

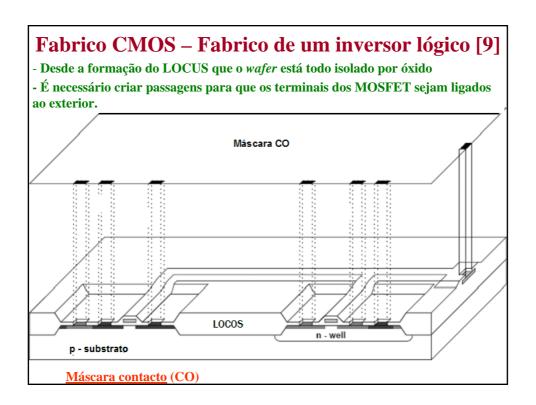

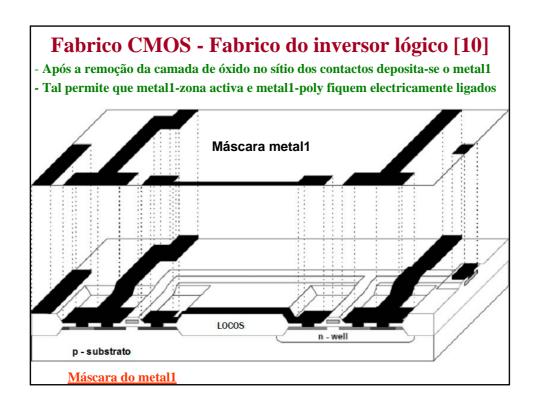

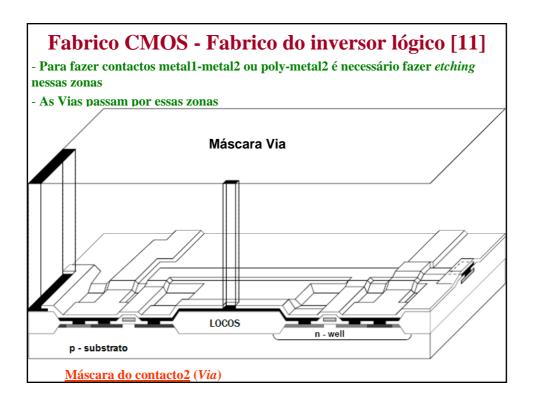

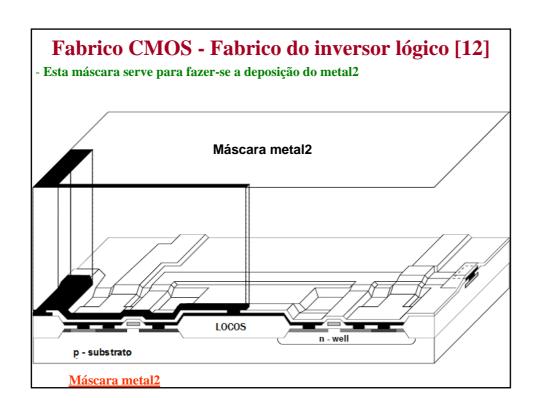

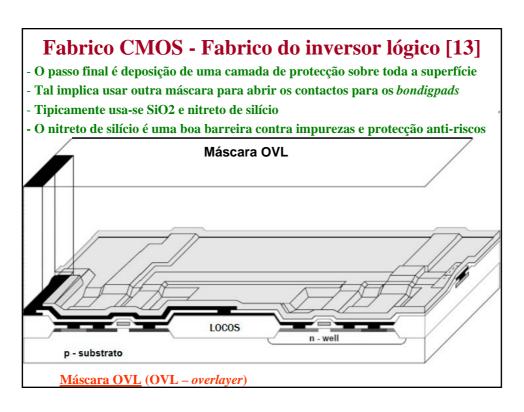

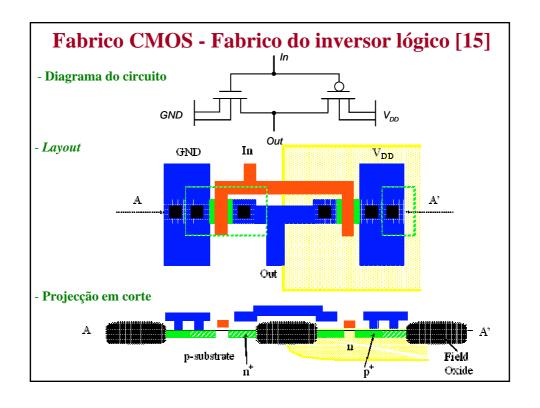

### Fabrico CMOS - Fabrico do inversor lógico [14] O dispositivo seguinte é o inversor lógico final. A - Bondingpad de Saída Drain do p-MOSFET G-B - Contacto do Substrato H - Gate do p-MOSFET Source do p-MOSFET C - Source do n-MOSFET Ι-D - Gate do n-MOSFET Contacto da n-well J -E - Drain do n-MOSFET Nó de entrada K -Nó de Saída LOCOS p - substrato

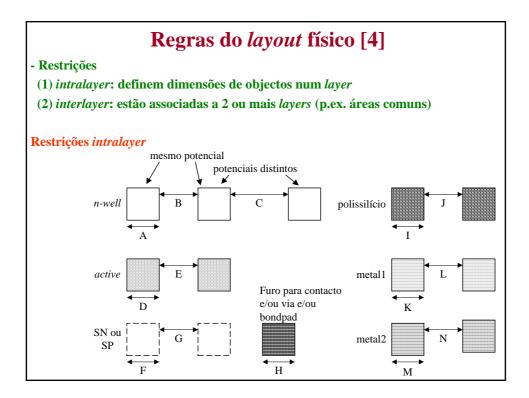

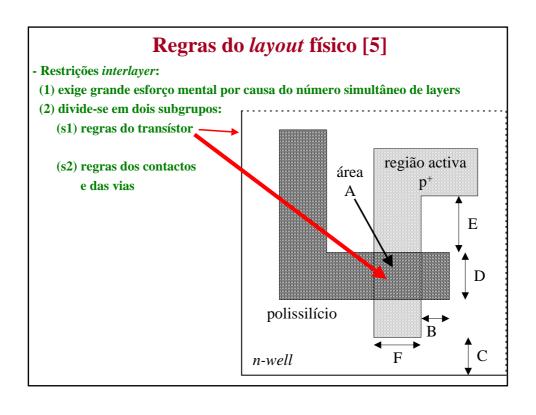

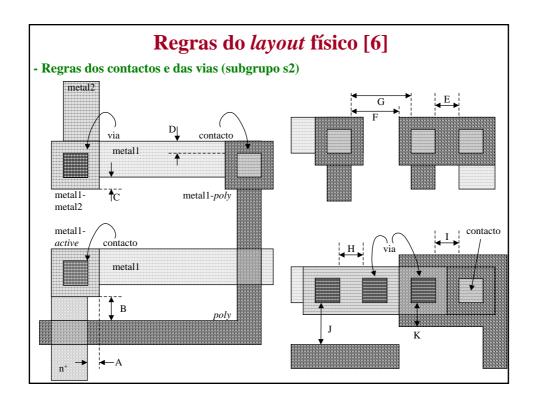

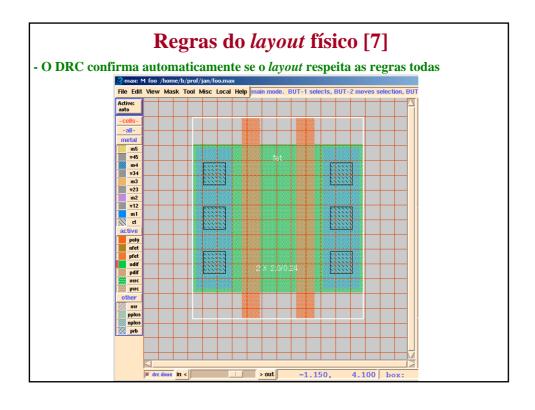

## Regras do layout físico [1]

- Resultam da necessidade de haver regras de desenho bem definidas para:

- (1) o fabrico ser praticável

- (2) obtenção das características desejadas dos componentes

- As regras do layout são um compromisso entre o projecto e o fabrico

- Se as regras forem respeitadas, a probabilidade de falha (ou funcionamento diferente do esperado) é mínima

- Em caso de falhas, o mais provável foi haverem falhas durante o projecto

- A titulo de exemplo, a regra mais simples consiste na largura mínima das linhas

- A largura mínima está associada á dimensão mínima da máscara cujo padrão é sem problemas transferido para a superfície do material semicondutor

- Normalmente, dois processos diferentes apresentam diferentes regras

## Regras do layout físico [2]

- Os processos CMOS mais usuais baseiam-se em 5 componentes fundamentais:

- (1) substratos tipo p (p-substrato) e/ou poços tipo n (n-well)

- (2) regiões de difusão (tipo n+ e p+)

- (3) pelo menos um nível de polissilício

- (4) pelos menos um nível de metal para interligar os componentes do microchip

- (5) contactos para interligação dos diversos níveis no microchip

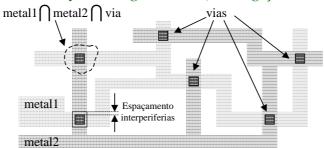

- Um *layout* é portanto:

- (1) combinação de poligonos de vários layers

- (2) a forma como os layers interligam entre si (ex. da ligação M1-M2 por Vias)

## Regras do layout físico [3]

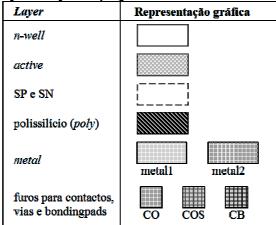

O layout associa uma cor ou tipo de preenchimento a diferentes layers

Layers mais utilizados no desenho de layout para fabrico de chips em

CMOS e respectiva representação gráfica.

- Active define as zonas onde vão ficar os dispositivos activos (MOSFETs)

- SP e SN define as zonas de dopagem p+ e n+ (repectivamente)

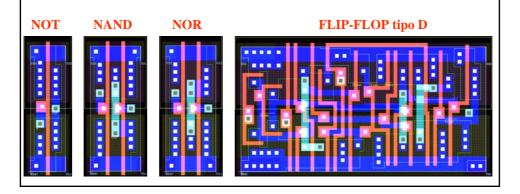

## Células standard [1]

- Surgem da necessidade de layouts densos (projecto VLSI) mas expeditos

- Incluem desde elementos lógicos simples (portas), passando por FLIP-FLOPs ou mesmo ALUs (unidades lógicas e aritméticas) de maior complexidade

- A grande vantagem é o estarem disponíveis em bibliotecas prontas a usar

- Conhecida a estrutura do CI é só (não é bem, mas!) posicionar os elementos

- Exemplo de células standard

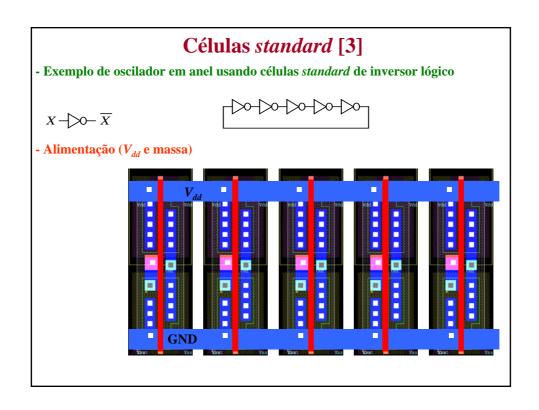

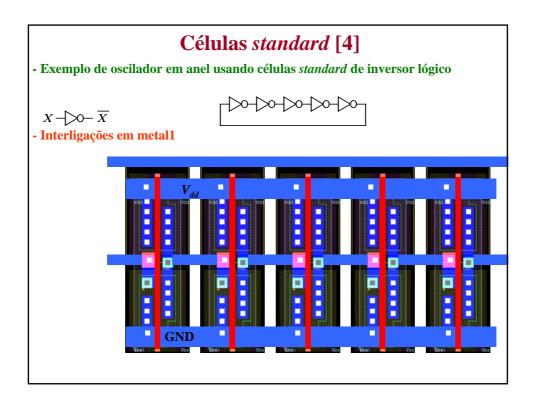

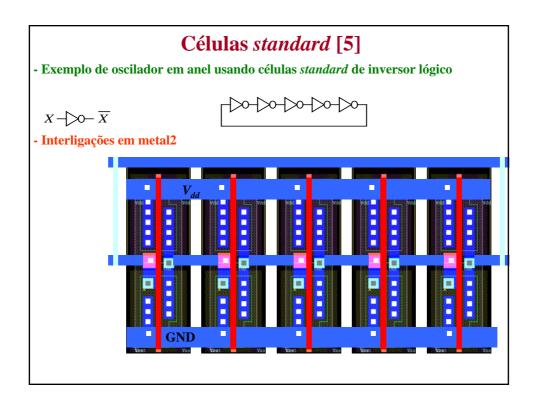

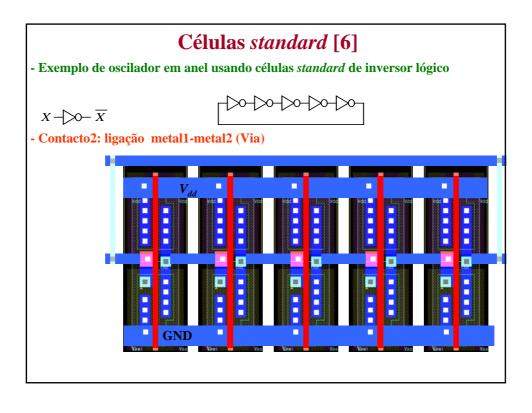

# Células standard [2] - Exemplo de oscilador em anel usando células standard de inversor lógico X → ∇ − X - Posicionamento

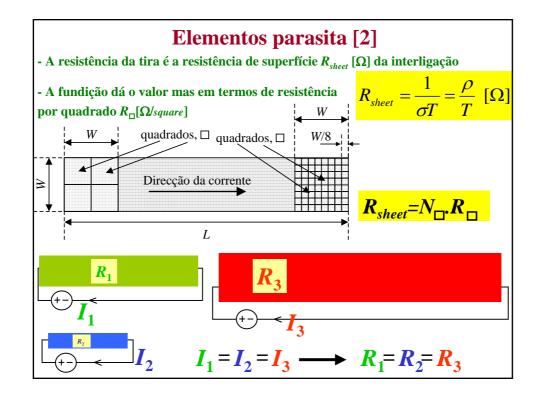

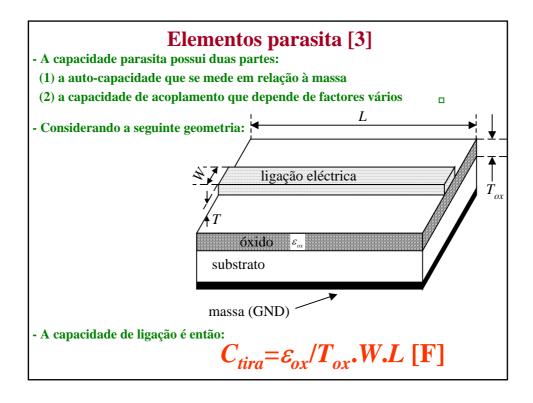

## Elementos parasita [1]

- São componentes eléctricos que surgem devido a fenómenos EM indesejáveis

- Os parasitas que mais limitam a performance de um microchip são

- (1) a resistência

- (2) a capacidade

- Uma forma comum de aferir o desempenho de um circuito digital é analisar as características de comutação, i.e., medir o tempo que demora a mudar o nível lógico na saída

- Existem ainda dois tipos de elementos parasitas, aqueles associados:

- (1) aos transístores (p.ex. capacidade entre portas) depende da tecnologia

- (2) às interligações eléctricas (os mais fáceis de tratar)

- As ligações são feitas recorrendo aos níveis de metal e polissilício

Que são depositados sobre dióxido de silício

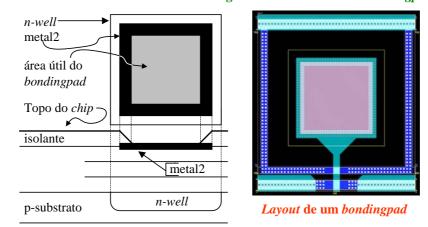

# Os bondingpads [2]

- A área de nitreto de silício a remover é ligeiramente inferior à do bondingpad

- A *n-well* providencia isolamento suplementar do *bondingpad* para o p-substrato

- No *microchip* deve-se rodear os *bondingpads* por dois aneis metálicos que ligam á massa e á alimentação, afim de minimizar os acoplamentos parasita